## Electrodeposition of Through Chip Copper Plug for Three Dimensional Packaging

Kazuo Kondo<sup>1</sup>\*, Jian-Jun Sun<sup>1</sup>, Takuji Okamura<sup>1</sup> Manabu Tomisaka<sup>2</sup>, Hitoshi Yonemura<sup>2</sup> Masataka Hoshino<sup>2</sup>, and Kenji Takahashi<sup>2</sup> \* E-mail: kkondo@cc.okayama-u.ac.jp <sup>1</sup> Dept.of Appl. Chem., Engineering, Okayama University 3-1-1, Tsushima-naka, Okayama, 700-0082, Japan

<sup>2</sup> Electronic System Integration Technology Research Department, Association of Super-Advanced Electronic Technologies (ASET)

1-6, Sengen 2-chome, Tsukuba, Ibaraki 305-0047, Japan

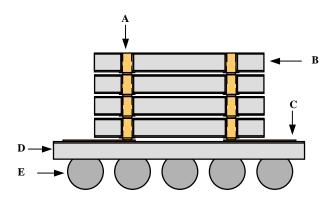

Recently three-dimensional (3D) packaging technology has attracted much attention because of the requirement of high density, high performance and lower energy consumption for the electronic devices. Thinned silicon chips down to  $50\mu m$  in thickness are stacked and shortest interconnection among them is offered by through chip copper plugs, and signal delay can be reduced to the lowest level (Fig.1) [1-3].

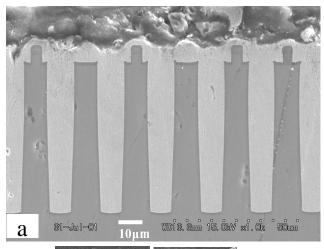

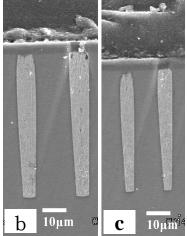

Sizes of the through plugs are in the range of  $50\mu m \sim 100\mu m$  in length and  $5\mu m \sim 20\mu m$  in diameter, which are 100 times larger in length than that of the Damascence, hence the mechanism of copper electrodeposition through chip plug might be different from that of Damascence copper process used for LSI interconnection [4-10].

In this presentation, factors to influence the bottomup filling in vias are discussed, including the additives' concentration, current density, via patterns and mass transfer. Under a proper electrodeposition condition, vias with depth in  $50 \sim 70 \mu m$  and square side in  $10 \mu m$ ,  $8 \mu m$ ,  $6 \mu m$  used for through chip copper plug were fully filled with void free (Fig. 2).

## Acknowledgments

The work was supported by NEDO as a part of the project of "Research and Development of Ultra Highdensity Electronics System Integration Technology".

## References

M. Koyanagi, T.Nakamura, K.W.Lee, Y.Igarashi, T.Mizukusa, Y.Yamada, T.Morooka, and H.Kurino, Advanced Metalization Conference, Montreal ,20 (2001).

M.Tomisaka, H. Yonemura, M.Hoshino, and K. Takahashi, Solid State Devices and Materials, Tokyo,40 (2001).

[3] K. Takahashi, The 2ed Annual Meeting on Electronic SI Technologies, ,Tokyo, 27(2001).

- [4] P.C. Andricacos, C. Uzoh, J.O. Dukovic, J. Horkans,

- H. Deligianni, IBM J. Res. Develop. 42, 567 (1998).

- [5] T.P. Moffat, J.E. Bonevich, W. H. Huber, A.

Stanishevsky, D.R. Kelly, G.R.Stafford, and D. Josell, J. Electrochem. Soc. 147, 4524 (2000).

[6] P. Taephaisitphongse, Y. Cao, A. C. West, J.

Elecotrochem. Soc.148, C492 (2001).

[7] K.Kondo, T.Okamura and Z.Tanaka, 'Effect of via opening width on Copper via filling electrodeposition', MES2001, Osaka, 95 (2001).

[8] K. Kondo, K. Hayashi, Z. Tanaka and Yamakawa, JIEP 3, 607(2000).

[9] K. Kondo and N. Yamakawa, ISTC2001, Shanghai , 532 (2001).

[10] K. Kondo, ECS Abstract 764, San Francisco, (2001).

Fig. 1 Schematic illustration of chip stacking for 3D packaging. (A) Through chip Cu plug (B) Thinning chip (C) Pad (D) Interposer (E) Solder ball.

Fig. 2 SEM of the cross section of completely filled vias used for through chip plugs on silicon chip with depth of  $50 \sim 70 \mu m$  and square of (a)  $10 \mu m$  (b)  $8 \mu m$  (c)  $6 \mu m$ .