## THE PROCESS OF INNOVATION IN BATCH FURNACES

Albert Hasper, Tanja Claasen-Vujcic, Renzo Noben ASMI

## Rembrandtlaan 7, 3723 BG Bilthoven, The Netherlands

Every introduction of a new technology node in the past decade has been accompanied by discussions on batch vs. single wafer tools. The end of the domination of batches has been repeatedly predicted and postponed. The current situation shows that batch furnaces are still holding a large market share. They still give the most cost-effective solution for LPCVD and diffusion applications and outperform single wafer tools in reliability. Batch furnaces are competitive, innovative, and companies continue to invest in their further development.

The objective of this abstract is to briefly address the latest process developments and ongoing improvements in cycle time and cost-effectiveness in batch processing.

In the past few years and particularly with the transition to 300mm wafers many new features have been innovated for batch furnaces [1]. New applications have been developed, such as Ultra Diluted Wet Oxidation and Poly Silicon Germanium, taking furnaces into deep submicron technology.

Ultra Diluted Wet Oxidation enables controlled growth of thin oxides in a wet ambient at elevated temperatures. The system is capable of controlling water vapour concentration from 0.1% up to 4%. Typical thickness uniformity obtained is 0.015nm (1 $\sigma$ ) for 1.5nm oxide thickness.

*Poly Silicon Germanium* layer can be grown in the batch furnace with excellent layer quality across the entire load of 100 or 150 wafers (Figure 2). In the A412 300 mm furnace from ASM it is possible to configure one reactor for oxidation and the other for Poly Si-Ge. The entire gate stack can be created and measured without wafers leaving the system.

Some other examples of ongoing process developments are implementation of injectors for LPCVD processes, very high temperature wafer annealing (1200°C) and selective HSG.

A different challenge presents combining low cost of ownership and short cycle time in one tool. Low cost of ownership is a stronghold of batch processing, cycle time of single wafer processing. To obtain a better market position, batch processing focuses on cycle time improvements, and single wafer processing on increasing throughput and reliability. In Table 1 some typical numbers for the A412 batch furnace are given for two processes. CpW takes all equipment related costs except yield losses into account. Cycle time is the raw cycle time: from FOUP in to FOUP out of the system. The throughput and the CpW numbers are up to several times better for batch processing. The total cycle time is up to 2 hours per step shorter for single wafer equipment (queue time included). This holds for a middle sized fab.

To improve the cycle time performance in the A412 furnace the following has been implemented:

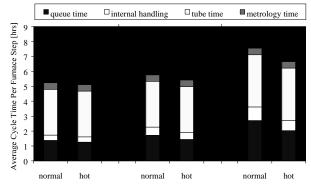

- *Integrated metrology*. A compact ellipsometer and particle counter enable measuring directly after processing. Typically 7% cycle time improvement is obtained in the furnace area.

- Fast temperature ramping

- *Predictive model-based temperature controllers* for excellent control of temperature ramp ups and downs and improved stabilization times.

## Flexible batch sizes from 25 to 200 wafers.

Large (200 wafer) load size means ultra high throughput and major cost benefits in memory fabs. In foundry type of fabs, small batch sizes provide cycle time benefits comparable to those of single wafer tools. Main gain in cycle time comes from reduction of queue time. This can be seen in Figure 2, where results of dynamic simulations of a fab with 5000 wafer starts per week and three different product flows is given. Approximately 20% reduction of cycle time can be observed when going from 100 wafer load size to 25 wafer load size.

Important to stress is that the very same furnace can be used for 25 wafer and 200 wafer load size, without any hardware changes, dependant on production needs. It is possible to use small load sizes during fab start up, and switch to larger load sizes during full production.

New features, such as integrated metrology and processing of small batches, as well as development of new applications, enable batch furnaces to keep their highly competitive position and extend their life-time into deep sub-micron technology.

## REFERENCES

- R. de Blank et al, European Semiconductor, May 2001, pp.29-31

- 2. R. Noben et al, ISSM, October 2001, pp. 411-414

Figure 1. Morphology of Poly Silicon Germanium layer grown in a batch furnace (100 wafers). Top, center and bottom wafer is shown. Ra = 2.5 nm.

| A412, 300mm batch furnace, 100 wf load            |             |            |            |

|---------------------------------------------------|-------------|------------|------------|

| Application                                       | Thrpt/ tube | CpW        | Cycle time |

| Gate oxide, 1.5nm                                 | 75 wf/hr    | 0,61 \$/wf | 2.5 hr     |

| Poly Si-Ge                                        | 40 wf/hr    | 4,50 \$/wf | 3.7 hr     |

| Table 1. Typical CpW and cycle time numbers for a |             |            |            |

selection of recipes. Refer to text for more details.

Figure 2. Cycle time break down for different load sizes in a fab with 5000 wf/week and 3 product flows. Dynamic simulations [2].