## Electrodeposition of Through Chip Copper Plug for Three Dimensional Packaging (2)

SeungJin Oh, Toshihiro Yonezawa, Kazuo Kondo, Manabu Tomisaka\*, Hitoshi Yonemura\*, Masataka Hoshino\*, and Kenji Takahashi\*

Department of Applied Chemistry Okayama University 3-1-1, Tsushima-naka, Okayama, OKAYAMA, 700-0082, JAPAN E-mail: <u>kkondo@cc.okayama-u.ac.jp</u>

## \*Tsukuba Research Center Electronic System Integration Technology Research Department, ASET Room C-B-5, Tsukuba Center Inc., Sengen 2-1-6, Tsukuba, IBARAKI, 305-0047, JAPAN

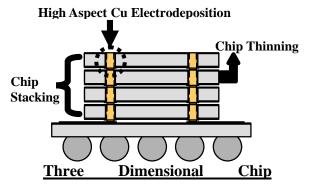

Through chip electrodes having high-aspect-ratio-vias (Fig. 1) are able to provide the shortest interconnection between chips, thereby reducing signal delay. For filling high-aspect-ratio-vias, copper electrodeposition was adopted because of good compatibility of copper to conventional multi layer interconnection in BEOL (back end of line process) of LSI [1, 2]. Previously we reported that filling vias with high aspect ratio, 10 µm in square and 70 µm in depth, used for through chip electrodes, was accomplished without void or seam in 12 hr of plating time [3]. With a optimzed electrodeposition condition by testing a series of electrodeposition conditions, perfect via filling of the electrode without overhang at via top was achieved by pulse reverse plating method as well as by increasing JGB concentration up to 20 mg/L in the plating bath, suggesting that bottom-up filling be markedly realized by adopting the above conditions. Yet, the plating time of 12 hr was not short enough to be used practically.

In this regard, for the purpose of accomplishing time-shortening with the use of a commercially-available bath and specially-designed ones, we are concerned with investigating copper pulse reverse plating to fill vias with the above-mentioned aspect ratio. We used the commercially-available bath containing CuSO<sub>4</sub> · 5H<sub>2</sub>O and H<sub>2</sub>SO<sub>4</sub> for basic bath, and PEG (polyethylene glycol), JGB (Janus Green B), SPS (Bis (3-sulfopropyl) disulfide) and HCl as additives. With this commercially-available bath of further optimized composition, electrodeposition time was shortened to 3.5 hr (Fig. 2) by adopting novel two-step electrodeposition method, i.e. by applying initial lower current of 2 mA/cm<sup>2</sup> for 2 hr and final higher current of 3 mA/cm<sup>2</sup> for 1.5 hr.

In the case of <u>specially-designed</u> baths, we firstly used four kinds of baths containing; (SPR A), (SPR B), (LEV A + SPR B) and (LEV B + SPR B). Here, SPR and LEV denotes suppressor and leveller, respectively. Baths containing SPR B showed better via filling abilities than others. Therefore, we chose LEV B as well as SPR B as DoE (Design of Experiment) parameters. With the partial help of a predictive model from DoE for electroplaitng time vs. addtives, we may optimize further the composition of specially-designed bath, in order to accomplish time-shortening of about 1.0 hr. Via-filling mechanism will be mentioned in the discussion section.

## **Acknowledgment**

This work was supported by NEDO as a part of the project of "Research and Development of Ultra High-density Electronics System Integration Technology". We appreciate support from EEJA (Electroplating Engineers of Japan Ltd.).

**References**

- 1. M. Koyanagi, T. Nakamura, K. W. Lee, Y. Igarashi, T. Mizukusa, Y. Yamada, T. Morooka and H. Kurino, in AMC 2001 (Advanced Metallization Conference 2001), p. 20, Montreal (2001).

- M. Tomisaka, H. Yonemura, M. Hoshino and K. Takahashi, in Solid State Devices and Materials, p. 40, Tokyo (2001).

- K. Kondo, J. J. Sun, T. Okamura, M. Tomisaka, H. Yonemura, M. Hoshino and K. Takahashi, ECS Abstract 538, Philadelphia (2002).

- K. Kondo, T. Okamura, J. J. Sun, M. Tomisaka, H. Yonemura, M. Hoshino and K. Takahashi, ICEP 2002, p.327, Tokyo (2002).

- 5. K. Kondo, K. Hayashi, Z. Tanaka and N. Yamakawa, JIEP 3, 607(2000).

- K. Kondo and N. Yamakawa, ISTC2001, p. 532, Shanghai (2001).

- 7. K. Kondo, ECS Abstract 764, San Francisco (2001).

Figure 1. Schematic illustration of chip stacking for 3D packaging.

Figure 2. SEM photograph of completely-filled through chip electrodes with  $10\mu m$  in square and  $70\mu m$  in depth for 3.5 hr.