## Saturation Current Model for the N-channel G<sup>4</sup>-FET

B. Dufrene<sup>1</sup>, B. Blalock<sup>1</sup>, S. Cristoloveanu<sup>2</sup>, M. Mojarradi<sup>3</sup>, and E. A. Kolawa<sup>3</sup>

<sup>1</sup> Department of Electrical and Computer Engineering, The University of Tennessee, Knoxville, TN, USA

<sup>2</sup>IIMEP, ENSERG, BP 257, BP 257, Grenoble, France

<sup>3</sup>Jet Propulsion Laboratory, Pasadena, CA, USA

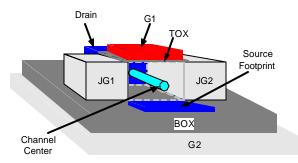

Abstract — A new saturation current model is presented for the n-channel G<sup>4</sup>-FET, a novel 4-gate transistor [1-2]. The model is verified against measurement results from G<sup>4</sup>-FETs fabricated using a commercially available 0.35-micron partially-depleted SOI process. A 3dimensional illustration of the G<sup>4</sup>-FET is shown in *Figure* 1. Since the  $G^4$ -FET is an accumulation-mode device, the conventional first-order JFET model [3] provides the basis for the G<sup>4</sup>-FET saturation current model. The JFET model's gate-to-source voltage is replaced by  $V_{JG}$ , the bias voltage applied to the G<sup>4</sup>-FET's junction (or lateral) gates. Then, to include the additional gate bias effects exhibited by the G<sup>4</sup>-FET's saturation I-V characteristics, the new model develops hierarchical equations for the JFET zero-bias saturation current parameter,  $I_{DO}$ , and the pinch-off voltage,  $V_P$ .

Figure 1. 3-dimensional illustration of the G<sup>4</sup>-FET.

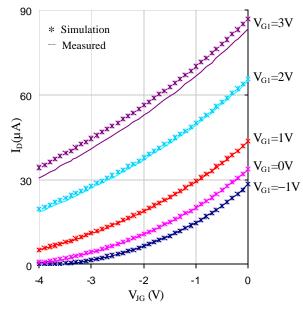

Parameter values for the new model were extracted using curve-fitting techniques. A plot of simulation (using the new model with extracted parameter values) versus measured I-V characteristics for a  $0.4\mu m/0.9\mu m$  n-channel G<sup>4</sup>-FET is provided in *Figure 2* for five different top-gate (V<sub>G1</sub>) bias conditions. The new model achieves very good accuracy for top-gate bias conditions ranging from depletion to weak accumulation. These and other systematic experiments confirm the model. A complete description of the model, along with verification, will be provided in the full paper.

*Figure2.*  $I_D$  vs.  $V_{JG}$  curves for measured and simulated 0.4 $\mu$ m/0.9 $\mu$ m n-channel G<sup>4</sup>-FET (V<sub>DS</sub>=4.0V).

## References

- B.J. Blalock, S. Cristoloveanu, B.M. Dufrene, F. Allibert, and M.M. Mojarradi, "The Multiple-Gate MOS-JFET Transistor," accepted for publication in the International Journal of High Speed Electronics and Systems, 2002.

- [2] S. Cristoloveanu, B. Blalock, F. Allibert, B. M. Dufrene, and M. M. Mojarradi, "The Four-Gate Transis tor," to appear in the 2002 Proc. of the European Solid-State Device Research Conf.

- [3] G.W.Neudeck and R. F. Pierret, Field Effect Devices, Second Edition, Addison-Wesley, Massachusetts, 1990, pp.16-22.