## **RAPID THERMAL SOLID PHASE EPITAXY ANNEALING FOR USJ FORMATION**

W.Lerch<sup>1\*</sup>, S. Paul<sup>1</sup>, D. F. Downey<sup>2</sup> and E. A. Arevalo<sup>2</sup> <sup>1</sup>Mattson Thermal Products GmbH, Daimlerstr. 10 D-89160 Dornstadt, Germany <sup>2</sup>Varian Semiconductor Equipment Associates Gloucester, MA 01930

Two of the key challenges according to the 2001 International Technology Roadmap for Semiconductors for the source/drain extension junction at the 65-70 nm node and beyond are to produce junctions between 10 and 19 nm with sheet resistance values between 760 to 830 ohm/sq. for low parasitic source/drain series resistance [1].

In contrast to fast spike anneals [2, 3] a simple approach for the formation of ultra-shallow junctions with boron consists of pre-amorphizing the substrate prior to dopant implantation and followed by a low-temperature (500-600°C, 10-30 min) solid phase epitaxial regrowth process in a standard furnace. The advantage of this technique is that boron changes over to the electrically-active substitutional site during the regrowth process while the diffusion within dopant the lattice is suppressed/minimized by the low temperature process. Numerous groups around the world are investigating lowtemperature solid phase epitaxial regrowth in furnaces.

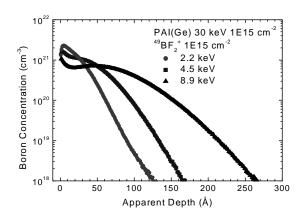

An alternative to spike anneals in rapid thermal annealing systems would be to run solid phase epitaxy processes in lamp-based systems with reasonable process times and in a tightly controlled ambient. This paper summarizes the latest results for low energy implants employing conventional beamline (B and BF<sub>2</sub>) wafers (with Ge preamorphization) with varying energies and doses in the Mattson 3000 Plus RTP system. The as-implanted <sup>49</sup>BF<sub>2</sub><sup>+</sup>- profiles in Ge pre-amorphized samples are shown in Figure 1. The Rapid Thermal Solid Phase Epitaxial process at 650 °C for 60 s itself is rather short and with a high throughput compared to above mentioned furnace anneals.

Comparable spike anneal data with the same implant conditions are also presented. The data are analyzed and discussed with respect to the sheet resistance versus junction depth metrics ( $R_S/X_J$ ) and compared to literature. These data as well as the uniformity results demonstrated on 200 mm wafers show the production-worthiness of the Rapid Thermal Solid Phase Epitaxy technology for the 65-70 nm technology nodes. This process also has the potential of extending Rapid Thermal Processing in conjunction with ion implantation beam line technology to the 65-70 nm technology node and perhaps beyond.

## REFERENCES

- 1. International Technology Roadmap for Semiconductors 2001, Semiconductor Industry Association

- 2. W. Lerch, B. Bayha, D.F. Downey, E.A. Arevalo: "State of the Art Techniques for Ultra-Shallow Junction Formation." *Rapid Thermal and Other Short-Time Processing Technologies II, Electrochemical Society Proceedings* **2001-9**, 312-336

- S. Paul, B. Bayha, W. Lerch, C. Merkl, D.F. Downey, E.A. Arevalo: "Production Worthy Repeatability of Spike Anneals." *IIT2002 conference*, Taos, New Mexico. Presented and accepted for publication.

Figure 1: As-implanted  ${}^{49}\text{BF}_2^+\text{-}\text{profiles}$  in a Ge preamorphized Si substrate.

<sup>\*</sup>Corresponding author: wilfried.lerch@mattson.com