## "Current Status and Future Prospects in Mixed Signal SoC"

## Akira MATSUZAWA

Advanced LSI Technology Development Center Semiconductor Company Matsushita Electric Industrial Co., Ltd.

3-1-1, Yagumo-Nakamachi, Moriguchi, Osaka, 570-8501, Japan E-mail: matsu@mrg.csdd.mei.co.jp

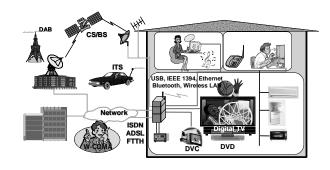

This paper reviews current status and future prospect in mixed signal CoC. Almost all the current electronics products have completed it's technology change from analog processing to digital processing. However input and/or output signals are still analog. Therefore, the mixed signal technology is essential to current electronics. In particular, these electronics products are going to communicate each other through digital networking. Metallic or optical wired networking and wireless networking will be widely used as shown in figure 1. Signal speed and carrier frequency have been increasing rapidly and receiving signal is used to be damaged. High speed or high frequency mixed signal technology is needed for addressing to this issue. Figure 2 shows the high speed mixed signal SoC for DVD recorder. This chip integrates 500MHz analog circuits and 16Mb DRAM to realize damage-free DVD recording and playback. It contains 24M transistors in 0.18um CMOS technology.

Analog circuit design is much difficult than digital circuit design. The number of specifications in digital circuits is small; such as delay, power dissipation, and area. In contrast, analog has many specifications; such as gain, band-width, distortion, noise, offset, phase margin, input impedance, impedance matching, etc. Designer should arbitrate and optimize the trade off between these many specifications. Furthermore total mixed signal system optimization becomes crucial. Conventional spice simulator is impossible to simulate and optimize the mixed signal systems. Concurrent simulation with SPICE, Verilog-D, and Verilog-A shall be used efficiently to address this new demand. This method can reduce the simulation time drastically, yet can keep sufficient accuracy. Accurate parasitic extraction and simulation becomes so crucial for high speed or high frequency circuits, that bottom-up design flow from layout and device level to system level is needed as well as top down design flow which is widely used in digital design. Noise and EMC simulation are also vital to predict the final performance. These simulation technologies will affect not only the design quality, but also total development cost and TAT.

The mixed signal technology impacts on process and device development. Analog characteristics of active device such as; accuracy, gain, mismatch, noise, and distortion must be addressed in process and device development for mixed signal SoC. Furthermore, passive components play important role in analog circuits. Resistor, capacitor, are widely used in conventional analog

circuits and inductor is needed for RF applications. The analog characteristics of these components often determine the final performance of analog circuits. Interconnection, substrate, and package also affect the noise figure of RF circuits, high frequency gain, isolation, and noise intensity from digital circuits, strongly. Thus we must pay much attention these passive elements which have been regarded as not important factors.

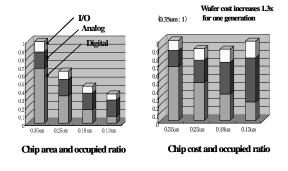

The process compatibility between these analog devices and digital devices becomes difficult. Furthermore, size of analog device can't be scaled down easily due to the difficulty of the reduction of operating voltage and keeping sufficient accuracy. Thus the cost of mixed signal SoC will increase with reducing technology node as shown in figure 3. New integration technology which can integrate scaled digital chip with not aggressively scaled analog chip should be developed.

Fig. 1 Image of future consumer electronics

Fig. 3 Chip area and cost estimation in mixed signal SoC Fig. 2 Mixed signal SoC for DVD recorder