## THIN FILM SPUTTERED SILICON FOR LOW TEMPERATURE WAFER BONDING APPLICATIONS

## R E Hurley, H S Gamble, S Suder and B M Armstrong Northern Ireland Semiconductor Research Centre School of Electrical & Electronic Engineering Queen's University Belfast Belfast, BT9 5AH, Northern Ireland, UK

There is a growing interest in low temperature bonding of silicon wafers to silicon and non-silicon substrates (1,2). Applications include MEMS, 3-D mm wave components, stacked layer devices, flexible silicon layers on plastic or metal, transfer of pre-processed silicon layers to nonsilicon substrates with large thermal expansion coefficient mismatches with silicon and silicon to sapphire. In many of these applications the bonding layer is required to have reasonable thermal conductivity and/or to be compatible with a silicon processing facility. Amorphous or polycrystalline silicon has long been used in integrated circuit manufacture, its thermal conductivity being an order of magnitude greater than that of silicon dioxide and hence appears to be the material of choice. We have used it extensively as a bonding layer in our silicon on silicide on insulator technology (3).

Polycrystalline silicon is normally deposited by LPCVD at 620  $^{\circ}$ C. Amorphous silicon can be deposited by LPCVD at 550  $^{\circ}$ C, but below this temperature the deposition rate is very slow. Thus for amorphous silicon deposition at low temperatures of around 300  $^{\circ}$ C, plasma enhanced CVD is normally employed. This material has a high hydrogen content, which is liberated again at temperatures above 500  $^{\circ}$ C. Thus during post bond anneals the liberated hydrogen produced large voids.

Attention was therefore directed towards sputtered silicon as a low temperature bonding layer for temperature sensitive substrates. RF magnetron sputtering was used to deposit silicon on oxidised silicon wafers. Initial work (4), showed that slow deposition rates produced layers with sub-nanometre surface roughness suitable for wafer bonding, but annealing bonded pairs at temperatures greater than 400 °C led to internal release of gas from the pores of the sputtered layer with consequent voiding and bond failure. The temperature at which this effect occurred was generally between 400 °C and 700 °C, but was essentially unpredictable. The effect could be overcome by annealing the deposited film before bonding at 1000 °C, suggesting that either gas had been driven out of the pores within the layer or that the pores had been closed by densification.

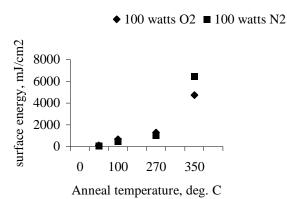

More recently the effect of oxygen and nitrogen plasmas on the sputtered silicon and oxide surfaces as a prebonding treatment has been investigated. The results show that: (a) after plasma treatment, the temperature at which voids first appear during annealing is consistent and increased from 400 °C to 600 °C; (b) a substantial increase in bond strength occurs when plasma treated bonded wafers are annealed at less than 400 °C. With suitable annealing cycles not exceeding 350 °C, bond strengths approaching the yield strength of single crystal silicon can be obtained, Fig 1. These results suggest indeed that sputtered silicon is a promising candidate for low temperature applications involving either temperature sensitive materials such as glass or plastics or where there is a large mismatch in thermal expansion coefficients such as metals or ceramics. In these applications post bond processing temperatures will be limited to less than 600 <sup>o</sup>C by other considerations. The technology should be compatible with Smart-cut layer transfer or room temperature mechanical splitting of ion-implanted wafers. For higher temperature applications, laser annealing to densify the sputtered silicon before bonding is being investigated.

Fig. 1 Effect of consecutive annealing cycles on bond strength (crack propagation method). Sputtered silicon to

oxide, 30 secs. plasma treatment before bonding.

## REFERENCES

- C. Perret, J. Boussey, C. Schaeffer and M. Coyaud, IEEE Transactions on Components and Packaging Technologies, 23-4, 665 (2000).

- D. Pasquariello and K. Hjort, IEEE Journal of Selected Topics in Quantum Electronics, 8-1, 118 (2002).

- H. S. Gamble, B. M. Armstrong, P. Baine, M. Bain, D. W. McNeill, Solid State Electronics, 45-4, 551 (2001).

- 4. R. E. Hurley and H. S. Gamble, Proceedings of the International Symposium on Ion Implantation and Other Applications of Ions and Electrons – ION 2002, Kazimierz-Dolny, June 2002, to be published in Vacuum.