## Effects of NH<sub>3</sub> Pre-deposition Anneal on ALD High-k Gate Stacks

Naim Moumen<sup>a</sup>, Jeff J. Peterson, Joel Barnett, Byoung Hun Lee<sup>a</sup>, Jong Hoan Sim, Robert. W. Murto<sup>b</sup>, Gennadi Bersuker and Howard. R Huff

> International SEMATECH 2706 Montopolis Drive Austin, TX 78741-6499 <sup>a</sup>Assignee from IBM <sup>b</sup>Assignee from Texas Instruments

The ITRS roadmap calls for implementation of high-k gate dielectric materials starting with the 65nm technology generation. This requires high quality interfaces between the high-k dielectric and Si substrate in the channel region. We have investigated the effect of various surface preparation treatments prior to high-k film deposition on transistor performance. Surface preparation treatments affect the growth of the high-k film and the final EOT.

This work discusses the effect of NH3 anneals and process conditions on high-k transistor performance such as gate leakage, Vt and electron mobility [1]. Transistors were fabricated on 200 mm p-type epi <100> Si substrate using a conventional silicon gate transistor process flow with thin high-k dielectrics deposited by the atomic layer deposition (ALD). The ALD-HfO<sub>2</sub> film exhibits an incubation period and island type growth on HF-last surfaces [2], and the resulting films exhibit high gate leakage current or non-working devices. The addition of an NH<sub>3</sub> pretreatment is shown to affect the properties of the interfacial layer at the silicon/high-k interface, which is critical for controlling the final EOT. An NH<sub>3</sub> anneal pretreatment, i.e., an NH<sub>3</sub> predeposition anneal (PreDA), after an HF-last clean led to ~5Å bottom interfacial layer after high-k deposition which is about 50% thinner than what was observed with the ALD films grown on the chemical oxides interfaces, without the NH<sub>3</sub> PreDA. Lower EOT and lower leakage current also are obtained when an NH<sub>3</sub> PreDA follows the HF-last for ALD HfO<sub>2</sub> films. These surface preparation processes result in an EOT reduction of 4Å to 5Å versus chemical oxides, providing a potential solution to achieving a sub-1nm EOT. NH<sub>3</sub> anneal temperatures ranging from 500°C to 900°C have been studied to correlate the effect of N concentration in the bottom interface on the transistor properties.

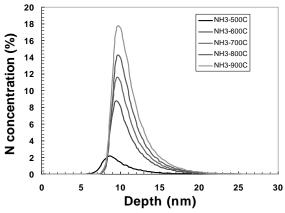

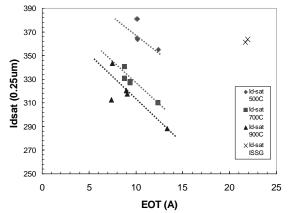

Figure 1 shows the nitrogen concentration obtained by SIMS analysis. The nitrogen concentration increase in a steady manner between 600°C and 900°C, while a rapid increase is observed between 500°C and 600°C. Figure 2 shows the drive current density versus EOT for different

transistors fabricated using different  $NH_3$  temperature anneal and a series of ALD-  $HfO_2$  film thickness (20Å, 25Å and 30Å. The data show an increase in drive current by using lower  $NH_3$  anneal temperatures or lower N concentration at the silicon/high-k interface.

Figure 1: SIMS nitrogen concentration profile after NH<sub>3</sub> anneal at different temperatures

Figure 2: Drive current versus different  $NH_3$  pre deposition anneal conditions obtained for the 30Å, 25Å, and 20Å ALD-HfO<sub>2</sub> with TiN electrode stack deposited on the HF-last/NH3 interface

## REFERENCES

- Naim Moumen, *et al*, Physics and Technology of High-K Gate Dielectrics - II, Eds. S. Kar, R. Singh, D. Misra, H. Iwai, M. Houssa, J. Morais, and D. Landheer, **PV 2003-22**, The Electrochemical Society Proceedings Series, Pennington, NJ (2003), p. 59.

- [2] M. Copel, M. Gribelyuk and E. Gusev, Appl. Phys. Letts., **76**, 436, 2000.