### **Strained Gate Dielectric**

T.Ikuta, S.Pidin, T.Sakuma, S.Doi\*, N.Tamura, N.Awaji\*, M.Kase and T.Sugii

Fujitsu Ltd., Advanced LSI Development Div., Fuchigami 50, Akiruno, Tokyo, 197-0833 Japan

\*Fujitsu Laboratories Ltd., 10-1 Morinosato Wakamiya, Atsugi, Kanagawa, 243-0197 Japan

### 1. Introduction

An aggressive scaling down of gate dielectric thickness is required for realizing ultra large scale integration. Nitrogen is incorporated in such gate dielectric to suppress a boron penetration and to decrease gate leakage current [1,2]. For the mobility enhancement, nitrogen distribution in gate dielectric has to be localized at the polysilicon - gate dielectric interface as in the case of nitrided because high oxide, concentration at the substrate interface introduces large amount of charge state and interface level [3]. In this work, we propose strained gate dielectric where strain is induced by interface nitrogen and show a correlation of the MOSFET carrier mobility enhancement with the gate dielectric - silicon substrate interface silicon atom (ISA) displacement.

## 2. Experimental

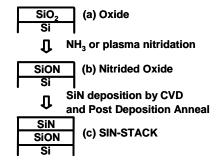

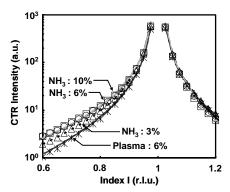

In Fig. 1 SIN-STACK fabrication flow is shown. Base oxide of 1.0 nm is formed, then the samples are annealed in NH3 ambient or plasma nitridation is performed, and then 0.2 nm of silicon nitride is deposited by CVD. Finally, post deposition anneal is applied. The ISA displacement was analyzed by x-ray crystal truncation rod (CTR) scattering [4]. CTR is the diffraction from the crystal surface where the vertical periodicity is truncated and the Laue condition is relaxed to a non integer value of Miller index for the vertical direction, which contains information of the local position of ISA determined from asymmetry of the CTR profile around Si(111) Bragg peak. We measured the intensity of CTR scattering by a high brilliance 3rd generation synchrotron radiation x-ray at SPring-8 facility. To examine the electrical characteristics of SIN-STACK, the 90 nm node CMOSFET with the gate length of 40 nm were fabricated [5].

# 3. Results and Discussion

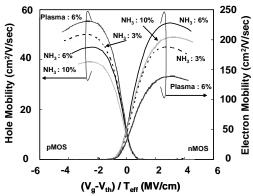

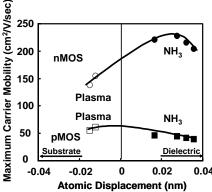

Fig. 2 shows carrier mobility for n- and p-MOSFETs in various conditions of NH<sub>3</sub> ambient or plasma nitridation. In general, higher nitrogen concentration degrades carrier mobility, because it causes higher charge and interface However, we found that higher nitrogen concentration does not always degrade carrier mobility, and carrier mobility depends on nitridation method at the same interface nitrogen concentration. Fig. 3 shows the asymmetry of the CTR profiles around Si(111) Bragg peak, and then we analyzed the ISA displacement. We correlate maximum carrier mobility with the atomic displacement in Fig. 4. The ISA displacement is defined relative to the ideal position of the bulk Si crystal where the direction toward gate dielectric is defined to be positive. The maximum mobility appears at ISA displacements of 0.025 and -0.005 nm for n- and p-MOSFETs, respectively. We speculate that nitrogen atom displacing ISA toward gate dielectric reduces interface level by terminating with dangling bond at the silicon substrate - gate dielectric interface. Nitrogen atom displacing ISA toward substrate generates interface level by breaking silicon atom bond. The ISA displacement is also successfully controlled for high-k gate dielectric.

### 4. Conclusion

We proposed strained gate dielectric structure. The ISA

displacement with SIN-STACK was measured by x-ray CTR scattering. We found out that it is possible to enhance mobility by ISA displacement caused by nitrogen introduction to the silicon substrate - gate dielectric interface. It is important to fabricate separate gate dielectrics for n- and p-MOSFETs, because the maximum mobility appears at ISA displacement of 0.025 and -0.005 nm for n- and p-MOSFETs, respectively.

### References

- [1] S. Tsujikawa et al., Symp. VLSI Tech., p.202, 2002

- [2] E. Morifuji et al., IEDM Tech. Dig., p.655, 2002

- [3] M. L. Green et al., J. Appl. Phys., p.2057, 2001

- [4] N. Awaji et al., Appl. Phys. Lett., p2669, 1999

- [5] K. Goto et al., IEDM Tech. Dig., p.623, 2003

Fig. 1 SIN-STACK structure and fabrication flow

Fig. 2 Carrier mobility for n- and p- MOSFETs

Fig. 3 CTR profiles with SIN-STACK

Fig. 4 Maximum carrier mobility with the ISA displacement