# Understanding and improvement of the SiGe wet selective etch for the sSOI manufacturing by the Smart Cut<sup>TM</sup> process

O. Rayssac <sup>(1)</sup>, P. Besson <sup>(2)</sup>, V. Loup <sup>(3)</sup>, C. Aulnette<sup>(1)</sup>, S. Favier<sup>(2)</sup>, B. Osternaud<sup>(1)</sup>, L. Portigliatti<sup>(1)</sup> and I. Cayrefourcq<sup>(1)</sup>

1- SOITEC - Parc technologique des Fontaines Bernin – 38926 CROLLES cedex- France.

2 - ST Microelectronics, 850 Rue Jean Monnet, 38921 Crolles, France.

3 - CEA-DRT – LETI/DTS – CEA/GRE -17 rue des Martyrs, 38054 Grenoble cedex, France.

# INTRODUCTION

The Smart Cut<sup>TM</sup> technology is a key technology for future high volume manufacturing of sSOI (strained silicon on insulator) wafers. The fabrication process involves : growing a strained layer of silicon on an underlying relaxed Si<sub>0.8</sub>Ge<sub>0.2</sub> layer, bonding of the strained layer to a receiving substrate, splitting at the implanted zone below the strained silicon layer and selective etching of the Si<sub>0.8</sub>Ge<sub>0.2</sub> remaining on the strained layer after splitting [1]. This final step is a key process to achieve a sSOI structure with a good thickness uniformity and a low surface micro roughness.

## **EXPERIMENTS**

Various chemical solutions  $(CH_3COOH/H_2O_2/HF, CH_3COOH/HNO_3/HF,...)$  [2], have been tested and compared. For the characterization, several techniques and tools have been used : optical microscopy, Atomic Force Microscopy (surface microroughness), ellipsometry (etch rate, selectivity and thickness uniformity), SIMS and VPD-ICPMS (Ge contamination of the surface).

### RESULTS

It has been shown that the  $CH_3COOH/H_2O_2/HF$  solution requires a delay between the preparation of the solution and its utilization [2]. Various possibilities in order to reduce this delay will be investigated.

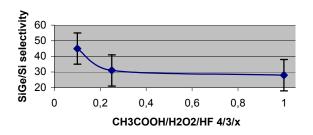

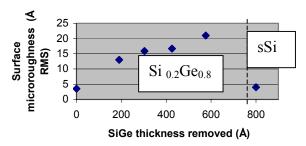

The influence of the solution in terms of chemistry and concentration (figure 1) on the selectivity and on the surface microroughness during the selective etch and after the complete removal of the  $Si_{0.8}Ge_{0.2}$  layer has been characterized. Figure 2 highlights that the surface microroughness value of the strained silicon layer is as low as the surface microroughness value before the selective etch.

The surface microroughness value for a  $1x1 \ \mu m^2$  scan length (1.3 Å RMS) is in the same range than the surface microroughness of a Si bulk, demonstrating that the wet selective etch does not damage the surface.

The impact of wet etchants on the revelation of strain field and cross-hatch patterns will be also reported.

After an appropriate cleaning in term of particle and organic contamination removal [3], the Ge concentration of the sSOI surface has been quantified. The value obtained (below  $10^{11}$  at/cm<sup>2</sup>) indicates that the sSOI surface is Ge free.

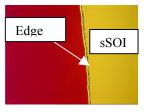

Microscopic observation has not revealed defects, as for instance edge delamination, induced by the wet selective etch (figure 3).

Other parameters such as thickness variation (for wafer and batch), dislocations density by TEM and strain value of the sSOI layer by Raman spectroscopy will be also reported to illustrate the overall quality of the manufactured substrates.

## REFERENCES

- 1. B. Ghyselen et al, *Proceedings. of the 3<sup>rd</sup> International Conference on SiGe(C) epitaxy and heterostructures*, 2003.

- T. K. Carns, M. O. Tanner and K. L. Wang, J. Electrochem. Soc., 142, p. 1260, 1995.

- F. Tardif, T. Lardin, P. Boelen, R. Novak and I. Kashkoush, Proceedings of the 3rd International Symposium on Ultra Clean Processing of Silicon Surfaces, p. 175, 1996.

$\label{eq:Figure 1} Figure \ 1: Si_{0.8}Ge_{0.2}/Si \ bulk \ selectivity \ versus \ HF \\ concentration.$

$\begin{array}{l} Figure \ 2: Surface \ microroughness \ evolution \ (40x40 \ \mu m^2) \\ versus \ Si_{0.8}Ge_{0.2} \ thickness \ removed \ for \ the \\ CH_3COOH/H_2O_2/HF \ 4/3/0.25 \ solution. \end{array}$

Figure 3: Microscopic characterization of the sSOI edge.