## HEAT TREATMENT EFFECTS ON THE I -V CHARACTERISTICS OF SILICON pn JUNCTIONS

Vasile V.N. Obreja, Alexandru Obreja<sup>x)</sup> National R&D Institute for Microtechnology (IMT), P.O. Box 38-160, Str Erou Iancu Nicolae 32B, 72996, Bucharest, Romania Tel: +401-490.84.12, Fax: +401-490. 82.38 e-mail: <u>vasileo@imt.ro</u> or <u>vnobreja@hotmail.com</u> <sup>x)</sup> POLICOLOR S.A. Company,

51, Av. Theodor Pallady, Bucharest, Romania Tel: +401-630.57.30, Fax: +401-321.22.72 e-mail:

graygold@mediasat.ro

Effects of reduction of the forward current, [1], or the reverse current, [2] after 400  $^{\circ}$ C annealing in H<sub>2</sub>/N<sub>2</sub> mixture are known for planar processed devices where inorganic dielectric films (SiO<sub>2</sub> and others) are used for junction passivation.

Similar effects have been found after short duration heat treatments at a temperature higher than 300 °C and normal atmosphere for mesa junctions with organic dielectric layer used for passivation, [3].

The purpose of this work is to present new experimental results revealing that by suitable thermal annealing significant reduction of the junction reverse current may take place on behalf of the surface component.

Experiments have been carried out on standard recovery silicon mesa PN junctions with positive beveling angle. The doping concentration of the starting silicon wafer was around of  $10^{14}$ /cm<sup>3</sup> and the area of the junction was of about 20 mm<sup>2</sup>. A thin silicon elastomer layer deposited on the silicon structure's peripheral surface after its cleaning followed by polymerization at 180 °C has been used as dielectric passivation layer.

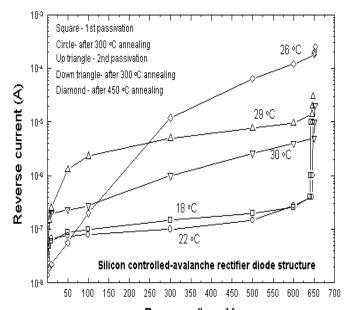

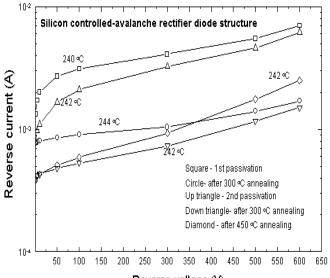

After a first passivation and after a 300  $^{\circ}$ C thermal annealing for about 4 hours, the I-V characteristics were measured. Then the silicone rubber passivation layer was removed from the structure peripheral surface and a second passivation has been performed. Again reverse I-V characteristics have been measured after this second passivation , after an another 300  $^{\circ}$ C thermal annealing and after an additional thermal annealing for half an hour at 450  $^{\circ}$ C.

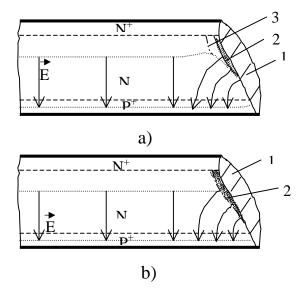

As one can see from typical results shown in Fig.1 and Fig.2, the surface component of reverse current may be the dominant current component even in the case when a saturation tendency is visible. Such a behavior can be understood taking into account electrical phenomena from the junction peripheral silicon dielectric interface (Fig.3). Square and circle symbol characteristics correspond to a surface inversion layer whereas down triangle and diamond symbol characteristics correspond to a surface accumulation layer. After short heat treatments, an increase of the reverse current is possible which is an undesired effect on the I-V characteristic.

By suitable junction passivation and short duration thermal annealing, power devices with an operating junction temperature higher than 200 °C can be realized. Weak surface inversion or accumulation layers are useful if only a surface depletion layer cannot be obtained.

## REFERENCES

[1] Sanden M.et all., Solid State Electronics,vol.43,1999, p.615

[2] Wang C.T., Solid State Electronics, vol.20, 1977, p.967[3] Obreja V., Solid State Electronics, vol. 44, 2000, p.49

Reverse voltage (V)

Fig. 1. Current-voltage characteristics near room temperature

Reverse voltage (V)

Fig.2. Current – voltage characteristics at high junction temperature

Fig.3. Surface junction inversion (a) or accumulation layers for a mesa silicon diode structure; 1- dielectric passivation layer; 2-inversion or accumulation layer; 3surface depletion region;