## 3-D Electromigration Simulation and Modeling in Copper - Low-K Multilevel Interconnect

V. Sukharev, R. Choudhury and C.W. Park LSI Logic Corporation, D-222 1621 Barber Lane, Milpitas, CA 95035, USA

Implementation of copper and low-K materials as major components of interconnect structures has resulted in the necessity to create new current design rules to ensure chip immunity to EM-induced failures. This practical demand causes an enormous interest in understanding the fundamental reliability properties of a copper dual-damascene metallization. Physically based models and simulations can be considered as powerful tools that can help to address this demand. Implementation of reliability simulation capabilities at the design rules generation step can help to avoid unnecessary conservative approaches, which reduce possible chip performance. To be able to reach this target a comprehensive simulation model of metal migrationinduced failure should be employed. In the general case detailed 3-D modeling should be applied. This is especially true for copper metallization characterized by a much lower critical stress for void nucleation than aluminum. The last fact clarifies an important role of nonuniform stress, current and temperature distributions in failure development.

In this study we have developed and solved a transient, 3D, fully-linked EM model. The developed model targets void nucleation and growth kinetics as a function of the segment geometry, interconnect architecture and the stress condition. We took into consideration all important atom migration causes: electron induced momentum transfer, time-dependent stress gradient, thermal diffusion, and concentration gradient. Implementation of the vacancy related diffusion mechanism has provided us with a capability to accurately implement a stress dependent atom diffusivity, which is different in different regions of the interconnect segment. The general character of the developed model has allowed us to investigate the effect of current direction as well as the effect of different loads: DC, AC and pulsed current on void nucleation and growth. Coupling of the electromagnetics, heat transfer, structural mechanics and atom migration models, based on a direct solution of the system of partial differential equations in the FEM environment, has allowed us to simulate stress-induced void nucleation and growth kinetics in different interconnect segments. We were able to observe real time void nucleation and growth kinetics. The latter has allowed us to compare our void dynamic based failure predictions with predictions made on the basis of simplified static models. We have demonstrated also the role of different atom migration driving forces in failure development. This paper provides some results of 3-D EM simulation in Cu - Low-K multilevel interconnect segments.

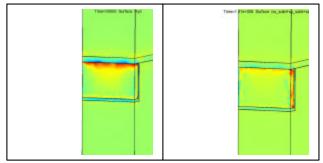

Fig.1. Evolution in the hydrostatic stress in Cu line caused by the atom migration.

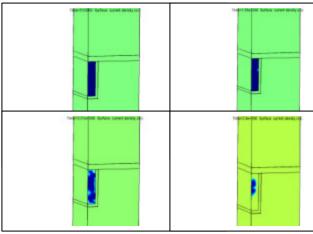

Fig. 2. Current distribution modification caused by the growing void (dark area represents the current path).

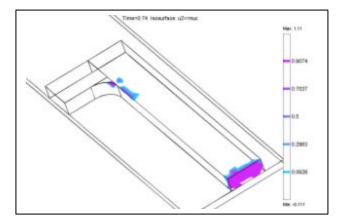

Fig. 3. Void distribution in the meander segment.

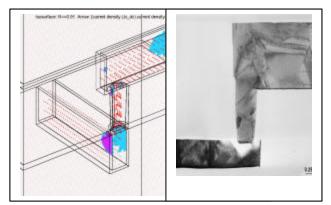

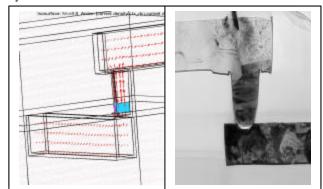

Fig. 4. Void nucleation in the Dual-Damascene structure caused by the down forwarded electron flow.

Fig. 5. Void nucleation in the Dual-Damascene structure caused by the up forwarded electron flow.

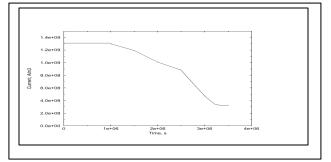

Fig. 6. EM-induced current reduction in Cu-line.