## Bondability of Plasma Hydrogenated Silicon Wafers

A.Y. Usenko<sup>1</sup>, W.N. Carr<sup>2</sup>, and B. Chen<sup>2</sup> <sup>1</sup>Silicon Wafer Technologies 240 King Blvd., Newark, NJ, 07102 USA <sup>2</sup>New Jersey Institute of Technology University Heights, Newark, NJ, 07102 USA

Layer transfer type SOI wafer processes as Smart-Cut [1], ELTRAN [2], Nova-Cut [3], Si-Sandwich [4] and others include bonding of a preprocessed wafer to a handle wafer. The preprocessed wafer should have a good quality of its surface (flatness, roughness, contamination, etc) to be bonded with reasonably high yield. Typically, the preprocessing decreases the bondability in most of the layer transfer processes. For example, high dose implantation required in Smart-Cut increase the wafer roughness and thus decreases bondability. We show that a layer transfer process that uses plasma hydrogenation of silicon wafers (Si-Sandwich) does not decrease the bondability. We also discuss possible mechanisms of wafer smoothening under plasma hydrogenation.

In this work various Si wafers were used as donors for layer transfer. The donor wafers were implanted with argon at 140 keV to a dose of  $1 \times 10^{15}$  cm<sup>-2</sup> in conditions that prevent amorphization of surface (wafer temperature was  $\sim 200^{\circ}$ C). The implanted wafers were annealed at 650°C in non-oxidizing atmosphere (argon). The annealed wafers were hydrogenated in plasma in two steps,  $\frac{1}{2}$  hr at 200°C, then 1/2 hr at 350°C. RF power was 300 W and hydrogen pressure was lower then 10 mTorr to increase a share of monatomic hydrogen in plasma. Further decreasing of hydrogen pressure was limited by oilcontaining backstream from vacuum pump. Samples hydrogenated at <1 mTorr pressure had hydrocarbon contamination on surface. Those wafers do not stick upon bonding. The handle wafers were thermally oxidized to a thickness of 200 nm of SiO2 to make hydrophilic oxide/Si bond. The hydrogenated donor wafers were bonded to oxidized handle wafers using regular bonding technique with Pirahna-clean surface activation. Some wafers were bonded using a plasma enhanced bonding process [5]. The prebonded wafer pairs were cleaved with either 500°C anneal, or with crack-opening technique [6]. Roughness of donor wafers after each processing step was analyzed with atomic force microscopy.

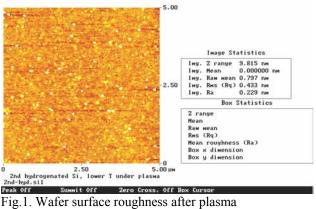

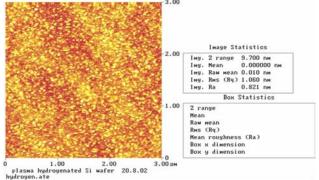

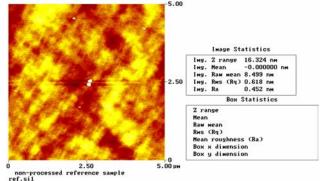

Figs.1-3 show AFM pictures of Si wafers. Initial wafers were purposely chosen with relatively high roughness (about 1 nm R<sub>aw</sub> mean while prime wafers have typically 0.2 nm R<sub>aw</sub> mean). The higher initial roughness allows easier monitoring of the roughness changes using AFM. Pictures show improving of wafer roughness after plasma hydrogenation to 0.79 nm  $R_{\rm aw}$  mean after hydrogenation at 200°C and further smoothening after hydrogenation at 350°C.

Layer transfer processes use different techniques to form a buried cleavage plane. Smart-Cut uses high dose hydrogen implantation. Implantation gives 2 peaks of damages - one at 1/2 of ion projection range, and another one on surface leading to surface roughening. ELTRAN uses epitaxy that typically results in surface covered with pyramid type defects that prevent bonding. Additional polishing is not applicable to heavy implanted wafers and restricts thinning of ELTRAN wafers. Our SOI process allows an annealing after implantation that removes implantation-induced surface roughening. Plasma hydrogenation further improves the surface roughness.

Mechanism of the improvement is somehow similar to mechanism of wafer smoothening by annealing in hydrogen [7], i.e. promoting surface diffusion of silicon atoms

hydrogenation at 200°C.

Peak off Summit off Zero Cross, off Box Cursor Fig.2. Wafer surface roughness after plasma hydrogenation at 350°C.

Summit Off Peak Off Zero Cross. Off Box Cur Fig.3. Initial wafer surface roughness at high magnification showing small particles on the surface. References.

- A.J. Auberton-Herve, C. Maleville "300mm ultra thin 1. SOI material using Smart-Cut technology" in Proc. IEEE SOI Conf. 2002 pp.1-5.

- 2. N. Sato, Y. Kakizaki, T. Atoji, K. et al. "Precise thickness control for ultra-thin SOI in ELTRAN SOI-Epi wafer" ibid. pp.7-10.

- J.T.S. Lin, J. Peng, T.-H. Lee, "Nova cut process: fabrication of silicon on insulator materials" ibid. pp.189-191.

- 4. A. Usenko, W.N. Carr, B. Chen, Y. Chabal "Alternative Smart-cut-like process for ultra-thin SOI fabrication, in Proc. Adv. Semicond. Manuf. IEEE/SEMI Conf. 2002 pp. 6-10.

- 5. K. Henttinen, I. Suni and S.S. Lau Appl. Phys. Lett. 76 (2000), p.2370.

- Q.-Y. Tong and U. Gösele Semiconductor Wafer 6. Bonding, Wiley, NY (1999).

- H. Moriceau, A.M. Cartier, B. Aspar, "Hydrogen 7. annealing treatment used to obtain high quality SOI surfaces" " in Proc. IEEE SOI Conf. 1998 pp. 37-38.