## High Performance P-Channel Schottky Barrier Thin-Film Transistors with PtSi Source/Drain

Ming-Hsien Lee<sup>1</sup>, Tiao-Yuan Huang<sup>1</sup>, Kuan-Lin Yeh<sup>1</sup>, and Horng-Chih Lin<sup>1, 2</sup> <sup>1</sup>Institute of Electronics, National Chiao Tung University, 1001 Ta-Hsueh Rd., Hsin-Chu 300,Taiwan <sup>2</sup> National Nano Device Laboratories, 1001-1 Ta-Hsueh Rd., Hsin-Chu 300, Taiwan FAX: 886-3-5722715; Email: hclin@ndl.gov.tw

Previously we have proposed and demonstrated a novel Schottky barrier (SB) poly-Si TFT with fieldinduced-drain (FID) extension [1]-[5]. CoSi<sub>2</sub> source/drain (S/D) was employed in previous device fabrication. The CoSi<sub>2</sub> S/D device is capable of ambipolar operation as the CoSi<sub>2</sub> material possesses a near-mid-gap work function. However, the CoSi<sub>2</sub> S/D device also suffers from low current drive because of the large barrier height. To improve the device characteristics, low barrier silicide materials, such as PtSi for p-channel [6] and ErSi<sub>2</sub> for nchannel [7], is needed. In this work, we fabricated and characterized devices featuring PtSi S/D. Compared to CoSi<sub>2</sub> S/D counterparts, significant improvement in pchannel performance is achieved.

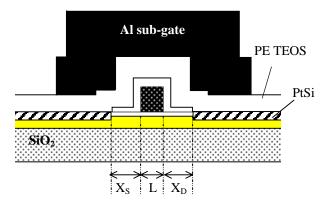

Figure 1 shows the cross-sectional view of a fabricated SB device with FID structure. Detailed process flow could be found in our previous reports [1][5]. In this study, the 50 nm-thick poly-Si channel layer was prepared by solid-phase crystallization (SPC). Gate oxide (15 nm) and passivation oxide (80 nm) were deposited by PECVD. Either PtSi or  $CoSi_2$  (i.e., control) was formed to serve as the metallic source/drain of the SB TFTs by the self-aligned silicidation (SALICIDE) scheme.

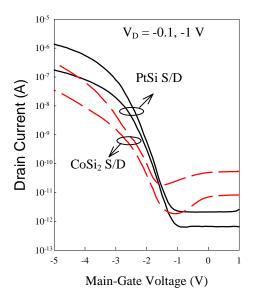

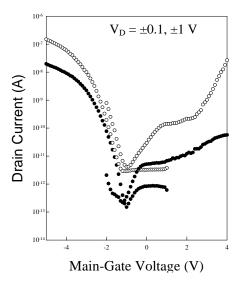

Figure 2 shows p-channel subthreshold characteristics of the devices with either CoSi<sub>2</sub> or PtSi S/D. It can be seen that the use of PtSi results in significant performance improvements including steeper subthreshold slope, larger on-current, and higher on/off current ratio. The higher on/off current ratio in the PtSi S/D device is a result of a higher on-current and a smaller off-state leakage current. The lower off-state current is ascribed to a larger barrier height for thermionic emission of electrons, which dominates the off-state conduction of p-channel operation [3]. In fact, the performance of nchannel operation for the PtSi S/D device is significantly degraded, as shown in Fig. 3. This is reasonable since the barrier height for electrons in PtSi/Si junction is extremely high (> 0.8 eV).

## References

- [1] H. C. Lin et al, in Tech. Dig. IEDM (2000), p.857

- [2] K. L. Yeh et al, SSDM, Tokyo, Japan, p.278 (2001)

- [3] K. L. Yeh et al, APL 79, pp.635-637 (2001).

- [4] H. C. Lin et al, IEEE EDL- 22, pp.179-181, (2001)

- [5] H. C. Lin et al, IEEE ED 49, pp.264-270 (2002).

- [6] W. Saito et al, JJAP 38, pp. L629-L631 (1999).

- [7] M. Nishisaka et al, JJAP 37, pp. 1295-1306 (1999).

Fig.1 Cross-sectional view of the SB poly-Si TFT.

Fig.2 P-channel subthreshold characteristics of SBTFT with CoSi<sub>2</sub> and PtSi S/D. (L/W =  $0.8/20 \mu$ m/  $\mu$ m, X<sub>S</sub>=X<sub>D</sub> =  $0.2 \mu$ m, and sub-gate bias = 4.5 V.)

Fig.3 Ambipolar subthreshold characteristics of SBTFT with PtSi S/D. (L/W = 5/20  $\mu$ m/  $\mu$ m, X<sub>S</sub>= X<sub>D</sub> = 1  $\mu$ m, and sub-gate bias = ± 4.5 V.)