Ge deep-submicron PMOS transistors with etched TaN metal gate on a High-K dielectric, fabricated in a 200mm prototyping line

M. Meuris<sup>a</sup> B. De Jaeger<sup>a</sup>, S.Kubicek<sup>a</sup>, P.Verheyen<sup>a,d</sup> J.Van Steenbergen<sup>a</sup>, G.Lujan<sup>a,d</sup>, E.Kunnen<sup>a</sup>, E.Sleeckx<sup>a</sup>, I.Teerlinck<sup>a</sup>, S.Van Elshocht<sup>a</sup>, A.Delabie<sup>a</sup>, R.Lindsay<sup>a</sup>, A.Satta<sup>a</sup>, T.Schram<sup>a</sup>, T. Chiarella<sup>a</sup>, R.Degraeve<sup>a</sup>,

O.Richard<sup>a</sup>, T.Conard<sup>a</sup>, J.Poortmans<sup>a</sup>, G.Winderickx<sup>a</sup>,

W.Boullart<sup>a</sup>, M.Schaekers<sup>a</sup>, P.W.Mertens<sup>a</sup>, M.Caymax<sup>a</sup>, W.Vandervorst<sup>a</sup>, E.Van Moorhem<sup>a</sup>, S.Biesemans<sup>a</sup>, K.De Meyer<sup>a,d</sup>, L.Ragnarsson<sup>a</sup>, S.Lee<sup>b</sup>, G.Kota<sup>b</sup>,

G.Raskin<sup>c</sup>, P.Mijlemans<sup>c</sup>, V.Afanas'ev<sup>d</sup>, A.Stesmans<sup>d</sup>, M.Heyns<sup>a</sup>,

<sup>a</sup>IMEC, Kapeldreef 75, B-3001 Leuven, Belgium <sup>b</sup>LAM Research Corp., Fremont, CA-94538, USA

<sup>c</sup>Umicore, B-2250 Olen, Belgium

<sup>d</sup>KU Leuven, Kasteelpark Arenberg 10, B-3001 Leuven, Belgium

The need for electron and hole mobility enhancement and progress in high-k deposition techniques, lead in the past years to a renewed interest in Ge substrate MOSFETs. Until now however all the transistor data published in the literature are exclusively for long channel transistors [1],[2] and [3]. But, before Ge devices can be used for advanced circuits, many issues of the Ge processing and device properties have to be addressed by fabricating them in conventional deep sub micron silicon like process. In the first place, the mobility enhancement of Ge vs. Si, as observed in long channel transistors, has to be proven to result in a larger drive current for short channel transistors. Secondly, it must be possible to manufacture these Ge devices in a silicon-like semiconductor-manufacturing environment. Last but not least, the reliability and yield of the Ge based circuits, has to be sufficient to allow ULSI circuits. This work builds on the results presented by [1], [2] and [3] and extends them to deep sub micron pFETs on 200mm wafers with standard DUV lithography and direct metal gate etch. A 3-mask process flow, compatible with a Si-process, for fabricating deep sub micron Ge PMOS transistors with directly etched TaN metal gate and HfO2 gate dielectric is presented for the first time and transistor device characteristics are analyzed. It is seen as a first step for the future exploration of the Ge based CMOS devices.

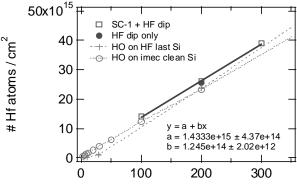

100mm and 200mm <100> 10  $\Omega$ .cm bulk Ge wafers were used, with specifications similar to those of Si device wafers. First, the HfO<sub>2</sub> deposition on a Ge surface was studied with Atomic-Layer CVD (ALCVD). In Fig. 1 the Hf growth curve as function of the ALCVD cycles and for different prepared Ge surfaces is shown. The steady growth rate is similar for Ge and Si substrates.

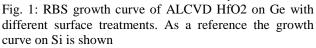

Also, capacitor and transistor structures were processed with a process flow, similar to silicon device structures. The gate stack consisted of a 10nm HfO<sub>2</sub> layer, with a metal gate of 10nm TaN thin film covered with a thick TiN layer. The HfO<sub>2</sub> deposition was performed with ALCVD at 300°C or Metal-Organic CVD (MOCVD) at 485°C. The surface was pre-treated with a 600°C NH<sub>3</sub> anneal [4,5]. After standard DUV litho, the gate was dry etched with a specially developed metal etch process, producing physical gate lengths down to 0.15mm while stopping on HfO<sub>2</sub>. In Fig. 2 a SEM picture shows the transistor structure made on Ge. Note the spacer formation to allow sub micron features.

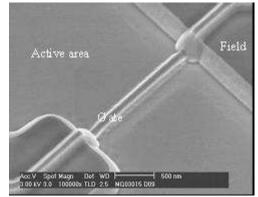

In Fig. 3 the  $I_D$ -V<sub>D</sub> characteristics of an 0.18 $\mu$ m Ge transistor with an HfO2 layer are presented. This result shows the feasibility of a Ge transistor device with short

gate lengths using a High-K deposited layer and a metal gate. Note for this channel length, the short channel effect, because more research is necessary for improved doping and activation in Ge processing.

## References:

[1] Chui, C.O. et al., IEDM'02, p.437 (2002)

[2] Shang, H. net al., IEDM'02, p.441 (2002)

[3] Huang, C.H. et al., Symp. VLSI Techn., p.119, (2003)

[4] Bai, W.P. et al., VLSI'03, p.121

[5] Van Elshocht, S. et al., accepted for MRS spring meeting 2004

# HO ALD reaction cycles

Fig. 2: SEM picture of the short-channel transistor structures made on Ge. Note the small gate feature (dry etched metal gate) and the spacer.

Fig. 3: Characteristics of a transistor made with a NH<sub>3</sub> pretreated 10nm MOCVD HfO<sub>2</sub> layer on Ge. Gate length is 180nm and gate width is 2 µm.