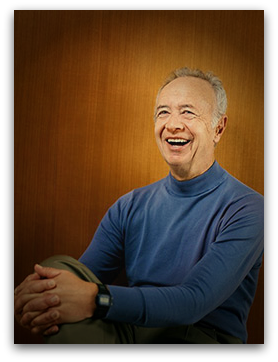

Businessman, author, and one of the foremost minds behind the development of the semiconductor, Andy Grove, passed away on Monday at the age of 79.

Businessman, author, and one of the foremost minds behind the development of the semiconductor, Andy Grove, passed away on Monday at the age of 79.

Technological giant

During his three decades with Intel, Grove helped transform the chip-making colossus into the world’s largest manufacturer of semiconductors. He grew with the company as it obtained more and more success, acting as Intel’s president in 1979 and becoming CEO in 1987.

“We are deeply saddened by the passing of former Intel Chairman and CEO Andy Grove,” said current Intel CEO Brian Krzanich in a news release. “Andy made the impossible happen, time and again, and inspired generations of technologists, entrepreneurs, and business leaders.”

Many considered Grove as one of the giants in the world of technology, leaving his mark on everything from memory chips to the digital revolution at large. Without Grove’s contributions to the development of the semiconductor, much of modern life would be very different. Items such as handheld electronics, LED displays, and even solar cells would not exist if not for the semiconductor.

(MORE: Learn about how semiconductors shape society.)

Grove’s influence on ECS

Here at ECS, Grove’s contributions to technology have helped shape some of our divisions and topical interest areas. In 2013, the Society established the Bruce Deal & Andy Grove Young Author Award to recognize the best paper published in the ECS Journal of Solid State Science and Technology (JSS) by a young author. The award was named in Deal, another Fairchild employee, and Grove’s honor for a seminal paper that was published in the Journal of The Electrochemical Society (JES) describing the Deal-Grove model, which is used to analyze thermal oxidation of silicon in semiconductor device fabrication and has had a lasting influence on the semiconductor technology industry.